Kioxia Corporation, a prominent player in memory storage solutions, has unveiled a breakthrough in transistor design aimed at making high-density, low-power 3D DRAM feasible for commercial use. The company detailed its progress on highly stackable oxide-semiconductor channel transistors during a presentation at the IEEE International Electron Devices Meeting (IEDM) in San Francisco on December 10. This development targets key challenges in modern computing, particularly in environments demanding vast data processing with minimal energy use, such as AI servers and Internet of Things (IoT) devices.

The announcement underscores a shift toward more efficient memory architectures as traditional DRAM approaches encounter scaling barriers. By stacking memory cells in three dimensions, engineers seek to boost capacity without proportionally expanding chip footprints. Kioxia’s innovations build on prior work, addressing both fabrication hurdles and power inefficiencies that have long constrained 3D DRAM adoption.

The Push for Next-Generation DRAM

Mounting Demands from AI and Data-Intensive Applications

Explosive growth in artificial intelligence workloads has intensified the need for DRAM that delivers greater capacity alongside reduced power draw. AI models, edge computing, and IoT sensors generate and process enormous datasets, straining existing memory systems. Conventional DRAM relies on planar layouts, where shrinking cell sizes hits physical limits dictated by lithography and material properties.

To counter this, researchers worldwide explore vertical stacking, layering memory cells to multiply density. However, implementation remains complex. Single-crystal silicon channels—standard in today’s DRAM—prove expensive to integrate in stacked configurations. Moreover, refresh operations, which prevent data loss in DRAM, consume more power as capacity scales, offsetting density gains.

Kioxia’s response evolves from last year’s IEDM disclosure of Oxide-Semiconductor Channel Transistor DRAM (OCTRAM). That prototype introduced vertical transistors using oxide semiconductors, promising better leakage control and lower refresh needs. This year’s update escalates the concept, demonstrating transistors suitable for multi-layer stacking.

Core Innovations in Transistor Stacking

Oxide-Semiconductor Integration for Vertical Scaling

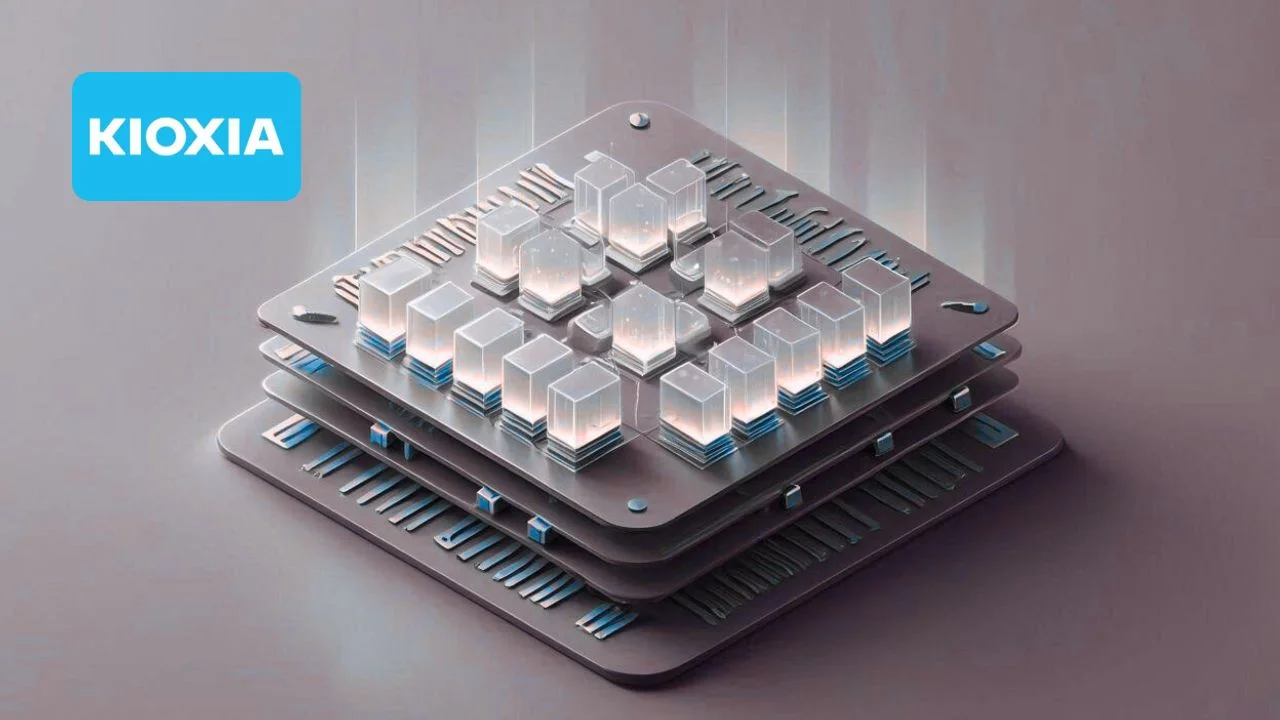

At the heart of Kioxia’s presentation lies a fabrication technique that stacks transistors horizontally within vertical layers. The process begins with established silicon-oxide and silicon-nitride films, forming a mature base structure. Engineers then selectively replace silicon-nitride regions with indium-gallium-zinc-oxide (InGaZnO), an oxide semiconductor known for its stability and low leakage.

This replacement method yields horizontal transistors aligned in vertical stacks, enabling dense 3D arrangements. Kioxia verified functionality in an eight-layer stack, a critical milestone showing reliable operation across multiple tiers. Such stacking circumvents the cost penalties of polycrystalline silicon alternatives, which suffer from grain boundaries that degrade performance.

A companion innovation redefines memory cell geometry. The team introduced a novel 3D cell structure that tightens vertical pitch—the spacing between layers—allowing finer scaling without compromising yield. These combined processes promise to make 3D DRAM economically viable, tackling a primary barrier that has kept prototypes confined to labs.

Electrical Performance Breakthroughs

Oxide semiconductors shine in off-state behavior, curbing leakage currents that plague silicon-based designs. Kioxia measured off-currents below 1 attoampere (10−18 A) in its horizontal transistors, paired with on-currents exceeding 30 microamperes (μA). These metrics translate to dramatically lower refresh power, essential for battery-constrained IoT and power-hungry AI data centers.

In demonstrations, the eight-layer transistor array operated successfully, with each level maintaining distinct electrical isolation. This confirms the structure’s scalability, as interlayer interference could otherwise erode reliability. Compared to conventional DRAM, where refresh power scales linearly with capacity, Kioxia’s approach decouples density from energy overhead.

Broader Implications for Memory Technology

Overcoming Historical Barriers to 3D Adoption

DRAM’s evolution mirrors the semiconductor industry’s relentless pursuit of Moore’s Law, but 3D stacking introduces unique fabrication demands. Traditional methods etch and deposit silicon channels layer by layer, inflating costs through complex tooling and defect risks. Kioxia’s oxide replacement sidesteps this by leveraging existing film stacks, adapting proven CMOS-compatible processes.

The low off-current also addresses a fundamental DRAM weakness: charge retention. Dynamic RAM cells store data as capacitors that leak over time, necessitating periodic refreshes. Oxide channels extend retention intervals, potentially slashing system-level power by 50% or more in high-density arrays, based on industry benchmarks for similar materials.

For B2B contexts, this matters profoundly. Hyperscale data centers running AI inference could see operational cost reductions, while IoT deployments gain longer battery life. Kioxia’s tech positions it competitively against rivals like Samsung and Micron, who pursue complementary paths such as 3D NAND extensions.

Path to Commercialization

Kioxia emphasized ongoing R&D to bridge lab results to production. Challenges remain, including yield optimization at higher stack counts (beyond eight layers) and integration with peripheral circuitry like sense amplifiers. Thermal management in stacked structures also warrants attention, as heat dissipation affects long-term reliability.

The company draws from its NAND flash expertise, where multi-layer stacking already exceeds 200 tiers. Adapting these learnings to DRAM could accelerate timelines, with prototypes potentially entering evaluation within 2-3 years. IEDM’s platform amplifies visibility, inviting collaboration with foundry partners and systems integrators.

Future Outlook and Industry Context

Kioxia’s disclosure arrives amid a memory market rebound, with DRAM revenues projected to grow 20% in 2025 per analyst forecasts, driven by AI chip demand. Competitors explore ferroelectric RAM (FeRAM) and magnetoresistive alternatives, but DRAM’s cost-per-bit edge endures. Oxide semiconductors, pioneered in display tech like LG’s OLEDs, now migrate to logic and memory, signaling material innovation’s resurgence.

This work aligns with industry roadmaps from JEDEC and imec, which prioritize 3D DRAM for sub-10nm nodes. Successful deployment could redefine server racks, enabling exabyte-scale AI training without proportional power hikes. For enterprise buyers, it heralds denser modules at lower TCO, reshaping procurement strategies.

About Kioxia

Kioxia is a world leader in memory solutions, dedicated to the development, production and sale of flash memory and solid-state drives (SSDs). In April 2017, its predecessor Toshiba Memory was spun off from Toshiba Corporation, the company that invented NAND flash memory in 1987. Kioxia is committed to uplifting the world with “memory” by offering products, services and systems that create choice for customers and memory-based value for society. Kioxia’s innovative 3D flash memory technology, BiCS FLASH™, is shaping the future of storage in high-density applications, including advanced smartphones, PCs, automotive systems, data centers and generative AI systems.